# TPMC533 32x ADC, 16x/0x DAC and 8x Digital I/O

### **Application Information**

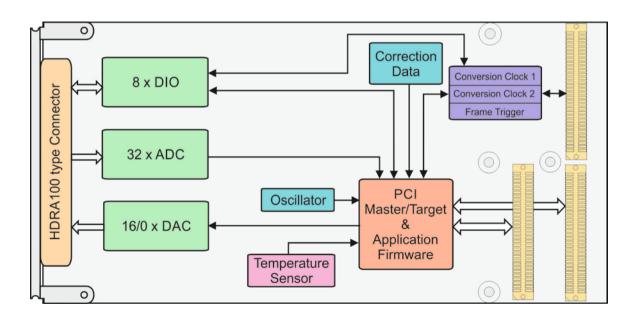

The TPMC533 is a standard single-wide PCI Mezzanine Card (PMC) compatible module providing 32 channels of simultaneous sampling true differential bipolar 16bit analog input, 16 or no channels of simultaneous update single-ended unipolar/bipolar 16bit analog output and 8 channels of tri-state 5V-tolerant TTL digital input/output. All signals are accessible through a HDRA100 type front I/O connector.

The PMC-Connectors P11 and P12 provide access to the control logic via a 32bit 33MHz PCI interface.

The ADCs offer true differential inputs with software selectable  $\pm 5\text{V}$  and  $\pm 10\text{V}$  bipolar input voltage ranges (one common setting for all eight channels of each ADC). The maximum sample rate of the ADCs is 200kSPS and they offer an oversampling capability with digital filter.

The DACs offer software selectable 0-5V, 0-10V, 0-10.8V,  $\pm 5$ V,  $\pm 10$ V and  $\pm 10.8$ V output voltage ranges (individual setting for each of the four channels of each DAC). The settling time is typically  $10\mu s$  and the DAC channels are capable to drive a load of  $2k\Omega$ , with a capacitance up to 4000pF.

Each TPMC533 is factory calibrated. The correction data is stored in an on-board serial EEPROM unique to each PMC module. These correction values can be used to perform a hardware correction of every analog-to-digital and digital-to-analog conversion. Additionally, measurement data read out of a temperature sensor on-board can be used to compensate temperature dependent errors.

The TPMC533 provides two Sequencers, one for AD Conversions and another one for DA Conversions. To perform periodic simultaneous conversions the conversion rates are programmable and can be output to other modules on PMC Back I/O Connector P14 or Front I/O Connector DIO pins for synchronization purposes. The TPMC533 can also operate as a target which means that the conversion rates can be sourced from P14 or Front I/O, created by another module.

A Frame Trigger signal, which can also either be generated by the TPMC533 and output on P14/Front I/O or generated by other modules and input from P14/Front I/O, can be used to synchronize ADC frames and DAC frames.

The signals on PMC Back I/O Connector P14 are ESD protected and driven or read by tri-state 5V-tolerant TTL buffers

To be able to collect ADC frames and to output DAC frames the TPMC533 provides input and output FIFOs. Data transfer on the PCI bus is handled by TPMC533 initiated block transfer mode DMA cycles with minimum host/CPU intervention.

TEWS TECHNOLOGIES GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners.

Issue 1.0.0 2017-12-05

# The Embedded I/O Company

The 8 Digital TTL tri-state I/O lines with  $4.7k\Omega$  pull resistors are ESD protected. The voltage, the pull resistors are connected to, is programmable by software and can be 3.3V, 5V, GND or floating level (one common setting for all eight Digital I/Os).

All 8 DIOs can be programmed whether to have their Digital I/O transmitters enabled or disabled individually per I/O line. The Digital I/O receivers are always enabled, so each DIO level can always be monitored and can generate an interrupt, triggered on rising edge, falling edge or both. Additionally, a debounce filter can be configured to get rid of bounce on the Digital I/O lines.

#### **Technical Information**

- Standard single-wide PCI Mezzanine Card (PMC)

- O conforming to IEEE P1386/P1386.1

- O Board size: 149mm x 74mm

- O 32bit / 33MHz PCI

- O DMA Master functionality

- 32 channels of simultaneous sampling true differential bipolar 16bit analog input

- O Input voltage ranges: ±5V and ±10V

- O Maximum sample rate: 200kSPS

- Oversampling capability

- 16 or no channels of simultaneous update singleended unipolar/bipolar 16bit analog output

- Output voltage ranges: 0-5V, 0-10V, 0-10.8V, ±5V, ±10V and ±10.8V

- O Settling time: typ. 10µs

- O load of  $2k\Omega$  with a capacitance up to 4000pF

- O Hardware Correction

- Factory calibrated

- O Temperature Sensor on-board

- O Programmable conversion rates

- O Can be output to other modules

- O Can be input from other modules

- Frame Trigger signal for synchronization purposes

- 8 channels of tri-state 5V-tolerant TTL digital input/output

- O ESD protection

- O HDRA100 type front I/O connector

- O Operating temperature: -40°C to +85°C

- O MTBF (MIL-HDBK217F/FN2 G<sub>B</sub> 20°C)

- O TPMC533-10R: 487000 h

- O TPMC533-20R: 497000 h

TPMC533 Block Diagram

TEWS TECHNOLOGIES GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners.

Issue 1.0.0 2017-12-05

# The Embedded I/O Company

#### **Order Information**

#### **RoHS Compliant**

TPMC533-10R 32 Channels of Simultaneous Sampling Differential 16 bit A/D, 16 Channels of Simultaneous Update

Single-Ended 16 bit D/A and 8 Channels of TTL Digital I/O, with HDRA100 front panel I/O

TPMC533-20R 32 Channels of Simultaneous Sampling Differential 16 bit A/D and 8 Channels of TTL Digital I/O, with

HDRA100 front panel I/O

For the availability of non-RoHS compliant (leaded solder) products please contact TEWS.

#### **Documentation**

TPMC533-DOC User Manual

#### **Software**

TDRV019-SW-25 Integrity Software Support

TDRV019-SW-42 VxWorks Software Support (Legacy and VxBus-Enabled Software Support)

TDRV019-SW-65 Windows Software Support

TDRV019-SW-95 Linux Software Support

QNX Software Support

For other operating systems please contact TEWS.

### **Related Products**

TA114 1.2 m Cable with one male HDRA100 Connector and two male HD50 Connectors

TA201 HD50 Terminal Block

TA313 Cable Kit for Modules with HDRA100 Connector

TEWS TECHNOLOGIES GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners.